Intel will launch a new processor codenamed Panther Lake in 2025

Beyond the unveiling of the 14th generation Core processor architecture, codenamed “Meteor Lake,” Intel further elucidated during the Intel Innovation Day that they are set to launch their subsequent Core processor in 2024, christened “Arrow Lake,” crafted using the Intel 20A process. Meanwhile, the “Lunar Lake” processor will be fashioned through the Intel 18A process. Additionally, Intel disclosed intentions to roll out a new processor product in 2025, codenamed “Panther Lake,” though the fabrication process remains under wraps.

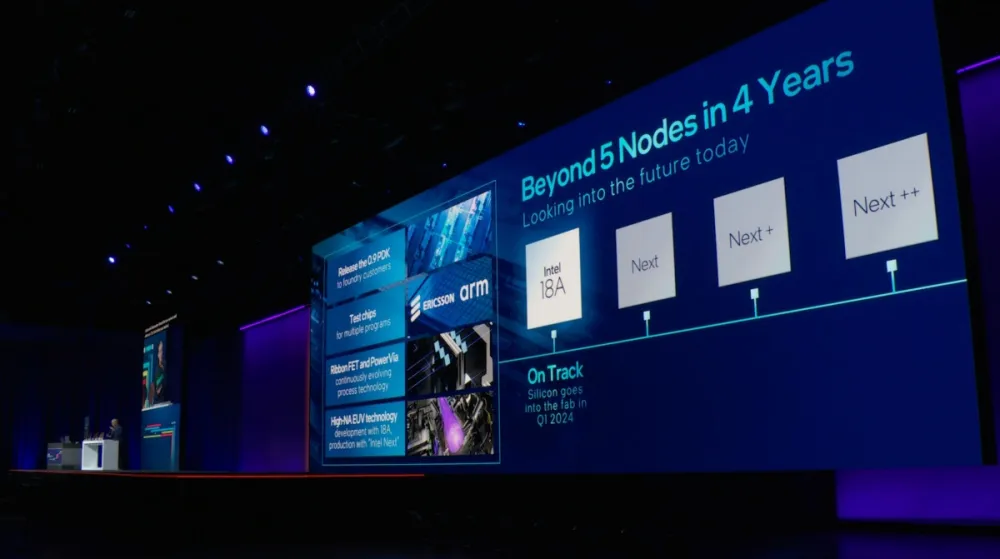

Within the revelations, Intel has augmented its previously declared fabrication roadmap by introducing three novel process nodes. However, these are provisionally designated as “Next,” “Next+,” and “Next++,” with launch timelines yet to be ascertained.

Barring unforeseen circumstances, the “Panther Lake” processor slated for a 2025 release is anticipated to utilize the “Next” fabrication technology, expected to accommodate a heightened transistor density within the same processor footprint, thereby bolstering computational performance and simultaneously curtailing overall power consumption.

As for the “Arrow Lake” processor, projected for a 2024 release and designed with the Intel 20A process, its inaugural test version has already been materialized. It stands as Intel’s premiere offering incorporating PowerVia back-end power delivery and the cutting-edge RibbonFET surround-gate transistor design. It’s projected that processors adopting the identical PowerVia and RibbonFET technologies within the Intel 18A process will seamlessly transition into mass production in the latter half of 2024.

Furthermore, Intel showcased a test chip package forged using UCle (Universal Chiplet Interconnect Express). They posit that the ensuing wave of Moore’s Law will evolve in tandem with advanced multi-chip packaging techniques. Presently, the UCle standard has garnered participation from over 120 industry entities. The displayed test chip package, conceived using the Intel 3 process, amalgamates the Synopsys UCIe IP chip crafted with TSMC’s N3E process and is encapsulated utilizing Intel’s EMIB technology.