Western Digital, Toshiba, and Intel all disclosed the development status of PLC flash memory technology as early as 2019. At present, Intel is more and more confident in the debut of PLC flash memory. The new flash memory can further reduce the price of SSDs, but Western Digital recently stated that SSDs using PLC flash memory are unlikely to appear before 2025.

According to a report by

TomsHardware, the use of PLC flash memory by Western Digital Mission only becomes feasible in the second half of this decade when SSD master control becomes more advanced, that is, after 2025. Of course, this is just their opinion, and other flash memory suppliers are tasked with 3D PLC SSDs entering the market and competing with HDDs in the next few years.

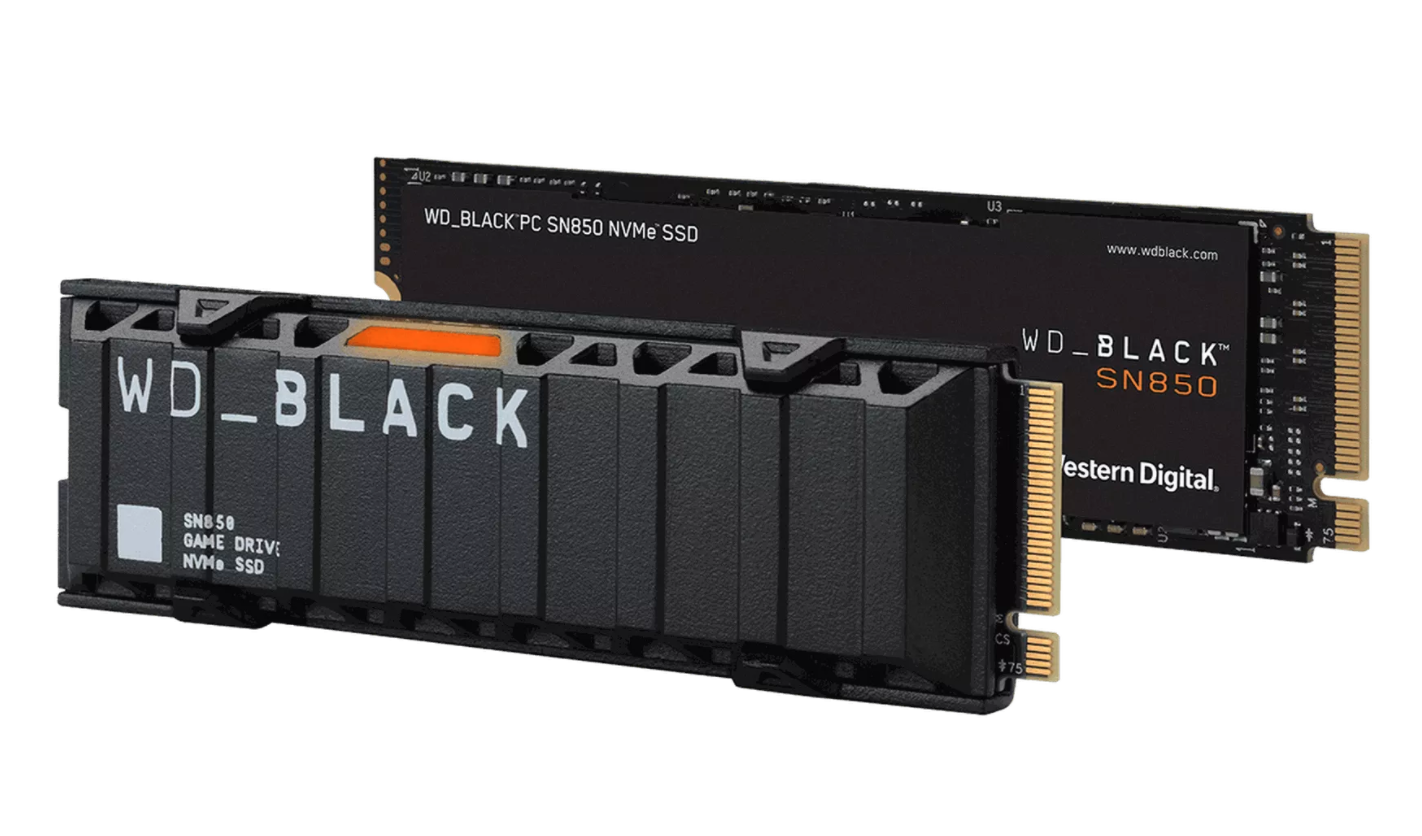

Image: Western Digital

“I expect that transition [from QLC to PLC] will be slower,” said Siva Sivaram, Western Digital’s technology and strategy chief, at Bank of America Merrill Lynch 2021 Global Technology Conference (via SeekingAlpha). “So maybe in the second half of this decade we are going to see some segments starting to get 5 bits per cell. We think that QLC across the broad segment will happen in the next [BiCS 6 generation, when] the majority of bits will switch over to QLC in the marketplace,” said Sivaram. “[…]In the next two years plus we are going to see the rapid acceleration of QLC adoption.”

Compared with QLC flash memory, PLC flash memory can store data from 4 bits to 5 bits per unit, and the relative number of levels has increased from 16 to 32, which can get a 25% increase in capacity. But in order to obtain this bonus, you need to pay more, you need a more powerful ECC, and a more powerful wear-leveling algorithm, which requires a more powerful SSD master.

At present, the main control used in 3D TLC SSD has provided high performance and durability. They use 120bit/1KB or even 340bit/2KB LDPC ECC algorithm. These algorithms are actually very complicated. In addition, it also needs to provide static and dynamic wear-leveling algorithms, EAID ECC, etc. to further improve the durability of the SSD

The main control of 3D QLC SSD needs to support 2KB or even 4KB LDPC ECC, as well as more complex wear-leveling algorithms. In addition, better SLC Cache algorithms are needed to improve SSD performance.