Linux Kernel to Tame PCIe 6.0/7.0 Heat with Intel’s New Driver

According to Phoronix, Intel’s open-source software engineers have been developing a PCIe bandwidth controller driver for the Linux kernel since last year, designed to automatically adjust the speed of PCIe links, with the driver recently entering its fifth iteration. The latest version of the driver makes adjustments for the thermal output of PCIe 6.0/7.0 interfaces by automatically reducing the link speed to mitigate heat generation.

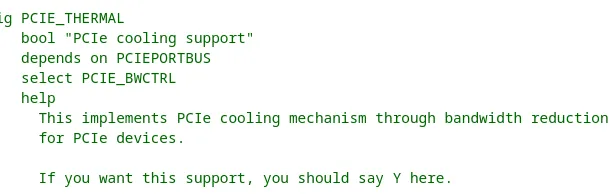

The new driver registers a “cooling device” for each detected PCIe port. If a port’s temperature exceeds the preset threshold, the software automatically lowers the link speed to reduce thermal output. Intel engineer Ilpo Järvinen noted in the patch description: “This patch series solely adds support for controlling PCIe link speeds. While controlling PCIe link width might also be beneficial, currently there appears to be no mechanism for this until PCIe 6.0 (L0p), hence no link width throttling functionality has been added in this series.” It is important to note that the new program is unrelated to the currently implemented PCIe 4.0/5.0 standards and is planned only for future higher versions.

The PCIe 6.0 standard (version 1.0) was publicly released in January 2022, benefiting data-intensive markets such as high-performance computing (HPC), data centers, edge computing, and artificial intelligence and machine learning (AI/ML). Compared to PCIe 5.0, it increases data transfer rates to 64 GT/s, with 16 lanes providing a maximum bi-directional bandwidth of up to 256 GB/s, and features lower latency. The PCIe 7.0 standard further enhances the transfer rate to 128 GT/s, with 16 lanes offering 512 GB/s of bi-directional bandwidth. It also focuses on optimizing channel parameters and coverage, continuing to achieve goals of low latency and high reliability, improving power efficiency, and maintaining backward compatibility with all previous generations of PCIe technology. The standard is currently at version 0.5, which includes the objectives, solutions, and architectural requirements of the PCIe 7.0 standard, as well as feedback from various relevant organizations.