AMD Ryzen 8000 “Strix Point” APU leaks

AMD has plans to launch the entirely new Zen 5 architecture in 2024, ushering in the Ryzen 8000 series, which will, unlike previous iterations, include products featuring a “big-little core” design. Among these, the APU code-named Strix Point employs the big.LITTLE design; its ES chip has previously appeared in benchmark test databases, revealing a configuration with 12 cores.

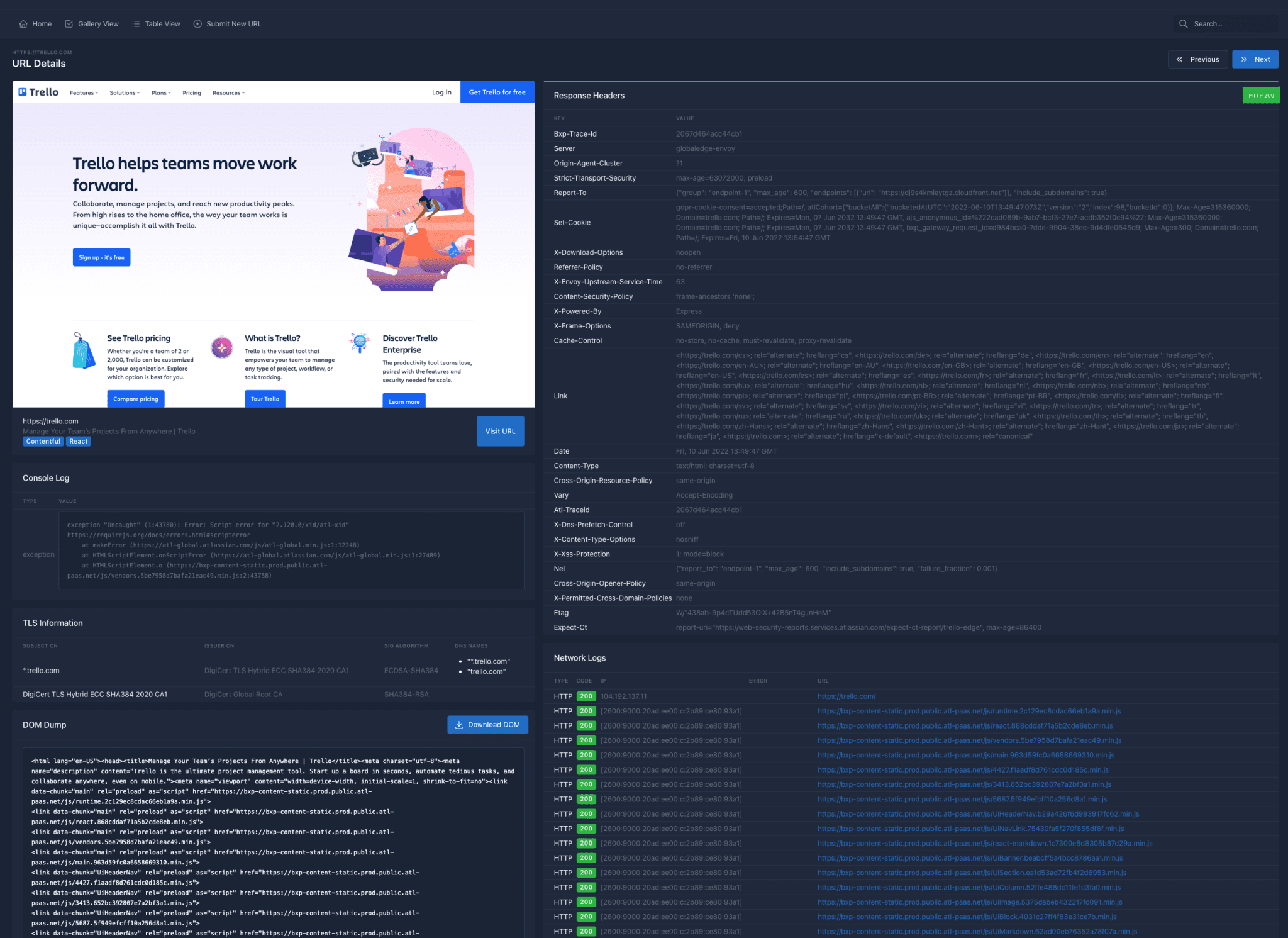

Recently, a website called “performancedatabases” exposed a CPU-Z screenshot of Strix Point, pertaining to a mobile processor. Though it was not possible to completely identify the processor’s specifications, the screenshot did allow the reading of compatible instruction sets and physical dimensions. Additionally, a screenshot from HWiNFO confirmed that the processor indeed belongs to Strix Point, manufactured using a 4nm process, with a TDP of 45W. Some information, however, such as the frequency—reaching an implausible 8.8 GHz—is inaccurate, but it’s worth noting that the processor supports AVX2 and AVX512 instruction sets.

More significantly, the software detected the processor’s core count. The screenshot illustrates that the CPU section includes four big cores of Zen 5 architecture along with eight little cores of Zen 5c architecture. Both sets support hyper-threading, differentiating this design from Intel’s small core architecture. Moreover, the L1 data cache size is 48KB, while the instruction cache size is 32KB. The performance cores possess a dedicated 1MB of L2 cache, while groups of four energy-efficient cores share 1MB of L2 cache.

Contrary to previous rumors that the L3 cache was 32MB, the screenshot reveals it to be 16MB. According to prior statements, Strix Point will also feature a 128-bit LPDDR5X memory controller. The GPU section’s CU count will increase to 16, based on the RDNA 3.5/3+ architecture, integrating an XDNA architecture AI engine with a computational power reaching 20TOPS. The launch is anticipated in either the second or third quarter of 2024.